磁性元件的一种最常见的形式就是电感,电感具有一定的感值因而随着频率的增加其阻抗也会随之增大,这点单独来看就可以作为一个一阶高频滤波器;当我们讨论的滤波对象由单一的电流通路(loop或者circuit – 回路)转变为两条或者更多条时,就需要至少在每条通路上放置一个电感才能达到同样的高频滤波效果 – 这点在实际的磁性元件上有非常简单而巧妙的设计刚好能满足,也即我们这里要谈到的共模电感(common mode choke),为什么呢? 因为当通路是多条时(比如最常见的两条),可以利用同向电流产生的磁通“共享”给另外一条电流通路,使其等效获得额外的阻抗,也即常说的(磁)耦合。由此,只需要在一个磁芯上绕制两个相互耦合的线圈绕组,就可以达到比使用两个单独电感更好的滤波效果。

以上引出了共模电感基本的功能特性,也即滤波。那么,首先需要区别开同样需要利用耦合工作的变压器和共模电感,因为滤波是对线路上的噪声进行抑制(或者吸收,后续详细介绍),从励磁方向来看是共模的,但是变压器是对代表着功率的电压激励电流进行传递,是差模的,因此类似安规电容的接法,共模电感需要处于Y接法(经地回路或者经参考地回路),变压器则处于X接法(跨接在输入输出回路上)。其次,其共模滤波效果的评估与测量本身需要借助额外的辅助回路,但是实际EMC(电磁兼容性)测试往往只测试由差模和共模共同导致的接收器(LISN – 线性阻抗稳定网络)端信号来判定是否符合对应的法规标准(比如CE认证),因此共模电感的作用往往不容易在规格书上找到答案,这也是工程师选型时往往借助经验而很难做仿真预测的原因。最后,细心的读者会发现共模电感名为电感却并不同于功率电感,既不考虑饱和电流更不做储能的考虑,并且英语名称是choke结尾的,所以其实其基本意义还是在于扼流(choke),后面会讲到,正是由于其扼流的效果才能达到滤波的作用,因此叫共模扼流线圈更符合其原理。

接下的篇幅我们来了解共模电感的基本结构原理,应用的分类以及相关的选型,希望对作为工程师的您有所帮助。同时,如果您对相关的介绍出现了疑问或者希望进行探讨,请与我们取得联系,我们的工程师团队会从元件与应用的角度为您提供尽可能的帮助。

1 磁场耦合

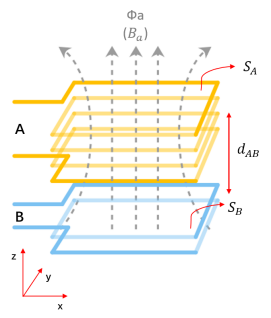

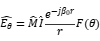

如图Fig.1所示,通电线圈A将在其电流回路(此处为线圈)附近空间分布磁场,用磁通量Фa (或者磁通密度 ) 来表示,其强弱程度取决于电流的大小,线圈的匝数,有效截面积,以及是否有磁芯,在其线圈中心位置处的磁通量近似可以表示为:

) 来表示,其强弱程度取决于电流的大小,线圈的匝数,有效截面积,以及是否有磁芯,在其线圈中心位置处的磁通量近似可以表示为:

其中,如果线圈中心有磁芯,则其磁导率 越大,其对应的等效磁路长度

越大,其对应的等效磁路长度 越短,同时必将使得磁通量越大。这是一个标准的电感结构与其对应的空间磁通量分布的情况,值得注意的是其磁通量分布情况并不依赖电流的变化,是恒等关系,其本质是由麦克斯韦电磁方程中高斯磁场定律推导而来。

越短,同时必将使得磁通量越大。这是一个标准的电感结构与其对应的空间磁通量分布的情况,值得注意的是其磁通量分布情况并不依赖电流的变化,是恒等关系,其本质是由麦克斯韦电磁方程中高斯磁场定律推导而来。

Fig.1 通电线圈A和B的空间磁场分布情况

当空间中另外一个线圈B以某种位置关系接近通电线圈A时(如图Fig.1),线圈B中必然会被部分由线圈A所分布的磁通量穿过,形成共享的关系。根据安培定律,当线圈B所包围的环路中磁通量发生变化时,则会在线圈B的回路上产生感应电动势,也即感应电压。可以预见,如果线圈B是一个不闭合的导电线圈,则无法形成回路电流,而只是在线圈B的两端形成感应电压,因为其回路上无电流则自然也不会产生对应的空间磁场;但是,如果线圈B是闭合回路,则一定会有回路电流产生,也即感应电流,同时,既然有感应电流则反过来会形成空间磁场分布,根据线圈B和线圈A的空间关系,线圈A必然也会分享到线圈B的分布磁通量,那么这样的相互感应最终会是怎样的一种结果呢?显然,如果线圈A只是恒定电流的话,则线圈B在固定位置上是不会感受到其分享到的磁通量发生了变化,因此只有当线圈A中产生变化电流(比如交变电流)是才可能发生彼此的相互感应。在一对一的情况下(仅看一个线圈对另外一个线圈的情况),感应电流总是产生对抗磁通变化的作用,因此对应的线圈B对线圈A的影响将刚好抵消线圈A共享给线圈B的磁通变化量,两者相互分享的磁通在变化量上将相互抵消。

磁场耦合在固定位置情况下(不同于电动机或者发电机),即是描述在交变电流情况下的,不同线圈之间因为共享磁通而产生的相互作用。作为功率转换或者信号隔离的变压器,或者用作电流补偿型的共模电感,都是这种磁场耦合情况。当设计或者生产某个共模电感时,总是不可避免的需要考虑一个问题:两个线圈究竟要保证哪些参数是必须满足要求的?或者说,除了电流和单边的感值外,有什么是需要考虑两者之间关系的必要要求?一种很常见的参数要求即是两边的感值误差必须足够小,或者有时提出耦合系数必须达到很高(比如>98%)。这是因为作为电流补偿型的共模电感,如果漏感过大,将会对差模信号产生明显的作用,要么造成不必要的差模阻抗(造成信号衰减或者差模带宽缩减),要么造成磁芯饱和而影响共模噪声抑制,因此,有必要对磁场耦合的耦合系数进行控制。

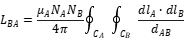

当两个线圈之间通过均匀磁导率的耦合媒介(磁芯)发生磁场耦合时,指定线圈A共享给线圈B的磁通量为 ,反之为

,反之为 ,则因为共享磁通量(磁场耦合)其对应的互感量可以分别定义为

,则因为共享磁通量(磁场耦合)其对应的互感量可以分别定义为 和

和 :

:

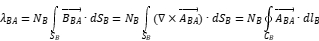

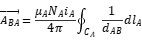

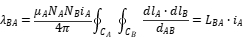

在感应线圈这端总共共享的磁通量也叫磁链(linkage, ),可以通过磁通密度

),可以通过磁通密度 和磁矢位

和磁矢位 之间的关系

之间的关系 表示为:

表示为:

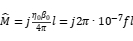

而位于线圈B上的每一点位置上由线圈A所分布的磁矢位是(在中心间距为 的平均情况下):

的平均情况下):

由此得到线圈A和线圈B之间的磁链:

因此得到线圈B作用在线圈A上的互感量 为:

为:

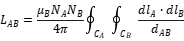

同样的道理可以得到 的表达式为:

的表达式为:

前面已经提到,两个线圈之间是通过均匀磁导率的耦合媒介(磁芯)发生了磁场耦合,因此 则显然:

则显然:

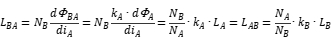

以上说明,绕制在同一个磁芯上的两个线圈,其互感量是相同的,用M来表示。以上证明过程详细可参考诺依曼公式(Neumann's formula)。现在,假设线圈A总共的磁通量 中共享的部分

中共享的部分 占比为

占比为 ,即

,即 ,同样线圈B的共享系数为

,同样线圈B的共享系数为 ,则会有:

,则会有:

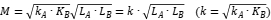

因此,由以上等式关系就可以得到两个线圈之间的互感量与各自独立的感量之间的关系:

以上就是磁场耦合系数k的由来:实际的共模电感可以通过分别测量两个线圈绕组的感值(另外一个线圈保持开路状态),以及漏感(另外一个线圈保持闭合状态, ),则对应的可以确定互感值和耦合系数k的大小。特别的,对于非常对称的绕制在高磁导率环形磁芯(比如MnZn Ferrite磁环)上的共模电感,两边绕组感值非常接近,漏感的大小将接近

),则对应的可以确定互感值和耦合系数k的大小。特别的,对于非常对称的绕制在高磁导率环形磁芯(比如MnZn Ferrite磁环)上的共模电感,两边绕组感值非常接近,漏感的大小将接近 ,可以看出,耦合系数越高,则漏感越低。

,可以看出,耦合系数越高,则漏感越低。

2 共模电感的应用

本文开篇已经提到,共模电感无非是同时跨接在两条电流回路上的一个电感,它的作用就是对可能存在于两个电流回路上的共模噪声进行抑制或者衰减吸收。但是,这两个并行电流回路并不限于组成差分回路的情形,比如一对电源线内的L线和N线,又或者是数据线端口上的D+线和D-线,基于共模噪声产生的原因,凡是共地的传输线之间都可能需要进行共模噪声的抑制。

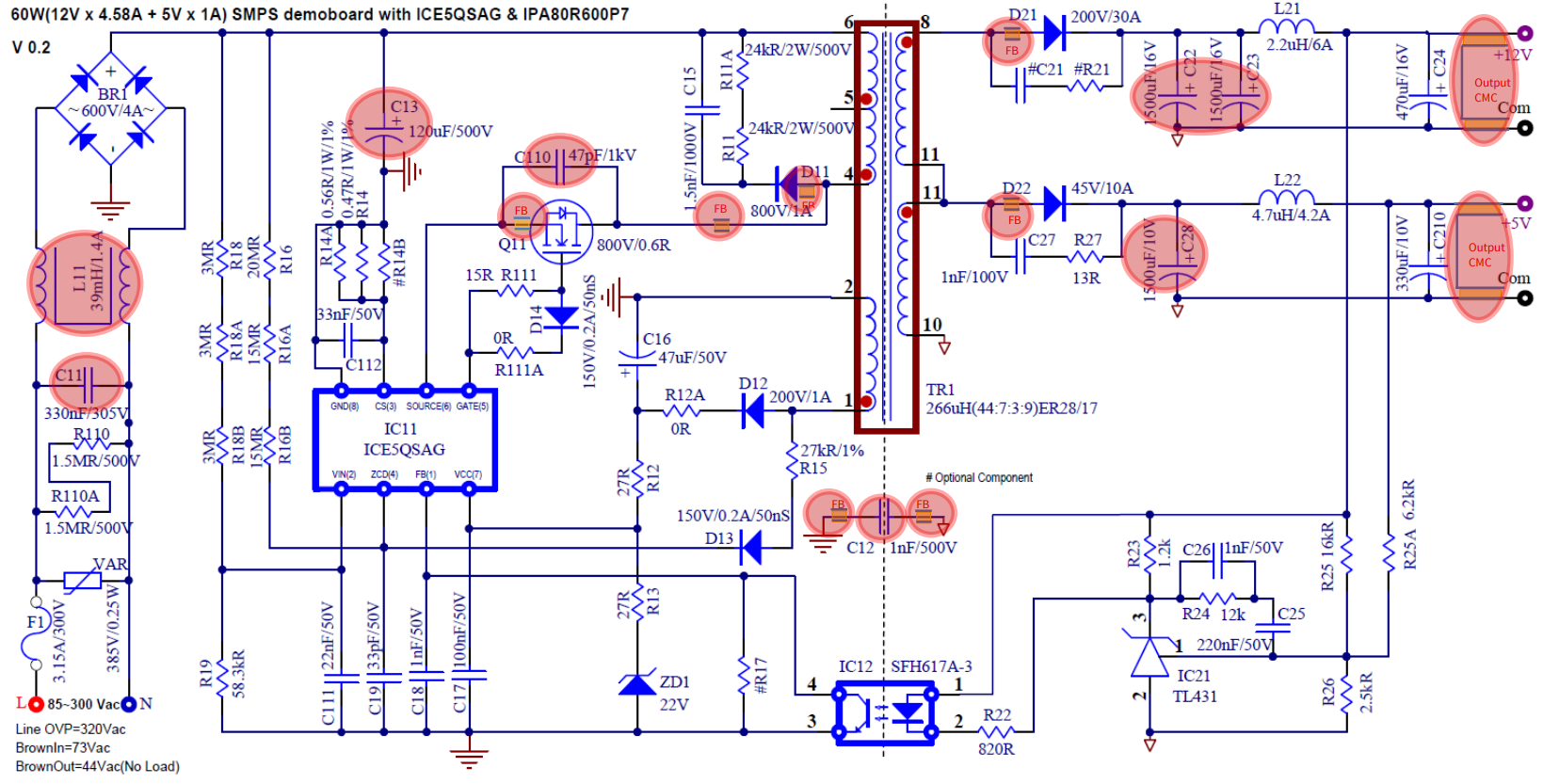

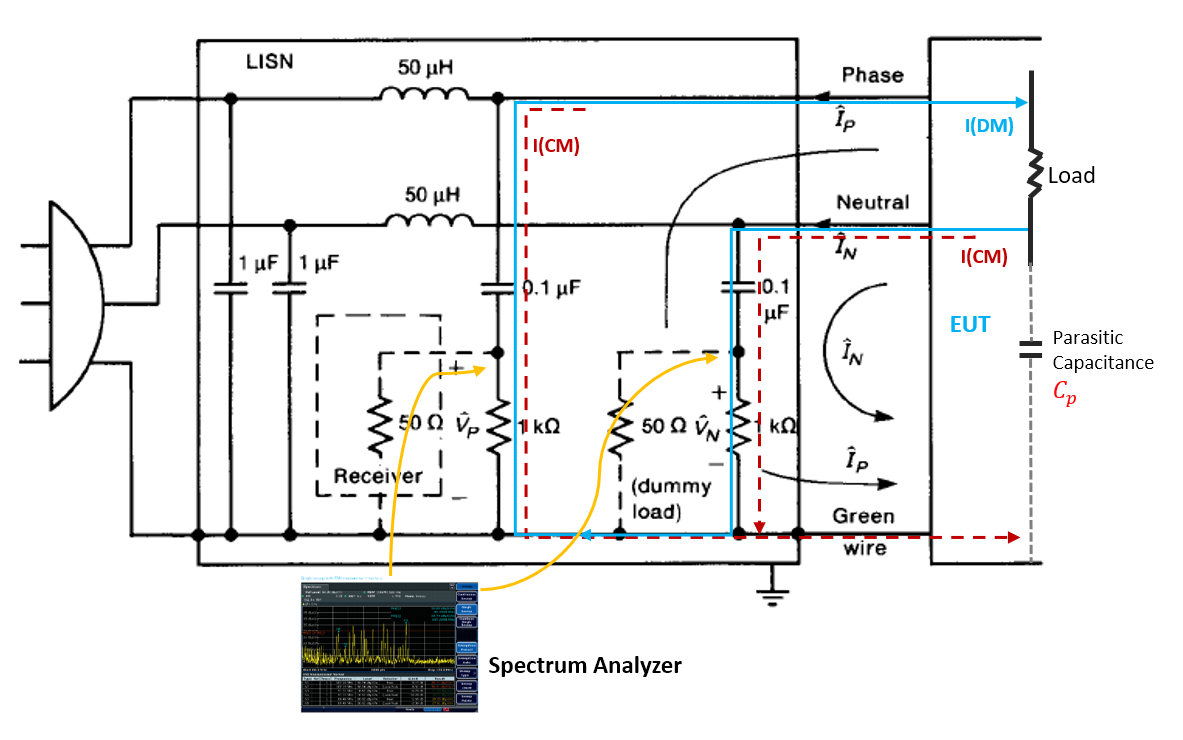

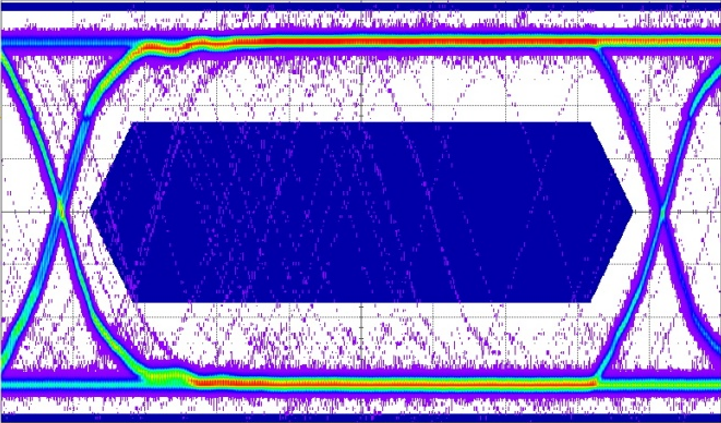

为了确定共模电感的应用,首先要明白共模噪声是怎么出现的:如图Fig.2所示(Infineon一款60W开关电源参考设计:DEMO_5QSAG_60W1),输入端为市电输入85~300Vac,电源端口上接线L,N和参考地之间构成了共地,实际上市电输入还有一根地线Green Line接到此参考地对接到物理地上。现在L线和N线构成电源回路并且跨接在此Flyback变压器的原边,作为主功率开关管的Q11的规格选用了800V的超节MOS管IPA80R600P7,其Rds(on)最大限额为600mΩ,为了有限散热一般会将散热媒介(铝散热鳍片)贴附在其外壳上,这样就增加了其高压管脚端对地的杂散电容,形成容性耦合将高压高频的输入端电压耦合形成噪音性质的电位势,在输入端口的L线和N线上通过参考地也会接收到此电位势,也即形成了共模噪声源。值得注意的是,容性耦合作为EMC测试中传导测试主要需要面对的共模噪声源广泛的存在于各种以AC-DC为主要形式的各种不同拓扑结构的电源,同时,在变压器的原边和副边其实存在非常多的小电流回路,每一个小的电流回路也同时会增加感性耦合的噪声电流,同样也会带来很难预测的共模噪声抑或是差模噪声,因此给EMC整改带来非常多的不确定性,这也是至今无法依靠仿真软件来做电磁兼容性仿真的原因。

Fig. 2 EMI对应策略元件示例(Infineon DEMO_5QSAG_60W1)

为了预估共模噪声的大小,通常需要假设共模噪声回路上的杂散电容量,一般在几十pF的等级。在图Fig.2的例子中,假设杂散电容量为20pF,当输入电源为230Vac,主功率开关管的开关频率为200KHz时开通关断总脉宽为1µs且上升下降沿分别为0.2µs则输入端最大电压为 V,交流输入经开关的占空比为

V,交流输入经开关的占空比为 ,在频谱密度分布上第一个转角频率为:

,在频谱密度分布上第一个转角频率为:

对应的在频谱密度分布上第一个峰值(1st harmonic第1个谐波)电压为:

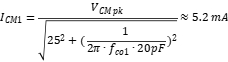

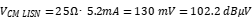

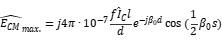

在共模噪声的回路上,在没有接共模电感的情况下,忽略串联等效阻抗(比如导线的电阻,寄生感量等)的情况下可以做最大的共模电流估算,如图Fig.3所示,在接入LISN(线性阻抗稳定网络)时其共模电流的大小为:

因此在LISN端口上的传导测试接收机(频谱分析仪)将接收到的共模噪声电压幅值将会是:

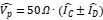

虽然实际的传到测试接收机上探测到的结果是:

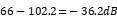

也即,共模噪声和差模噪声的幅值叠加出来的,但是显然只要共模得到抑制,则最终的测试结果将会得到改善。因此,比如在常规的通信和工业类应用EMC标准EN55022中,在150KHz到500KHz上幅值QP必须低于 ,因此此处必须对共模噪声进行最大

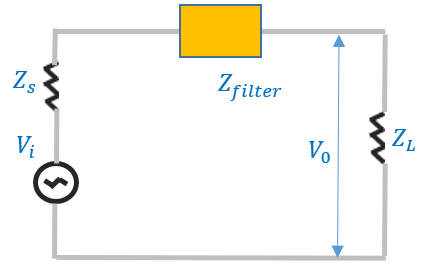

,因此此处必须对共模噪声进行最大 的衰减。取-20dB的衰减目标为例,通过简单计算,在共模回路上主要的阻抗为杂散电容的阻抗,大约在25KΩ,如图Fig.4所示对应的需要的共模阻抗约为250KΩ,换算为一颗125mH的共模电感。

的衰减。取-20dB的衰减目标为例,通过简单计算,在共模回路上主要的阻抗为杂散电容的阻抗,大约在25KΩ,如图Fig.4所示对应的需要的共模阻抗约为250KΩ,换算为一颗125mH的共模电感。

Fig.3 EMC测试中传导测试示意图(共模噪声和差模信号的回路示意)

Fig.4 滤波器插入损耗的回路(左) 与 对应的衰减幅度和滤波器阻抗的关系(右)

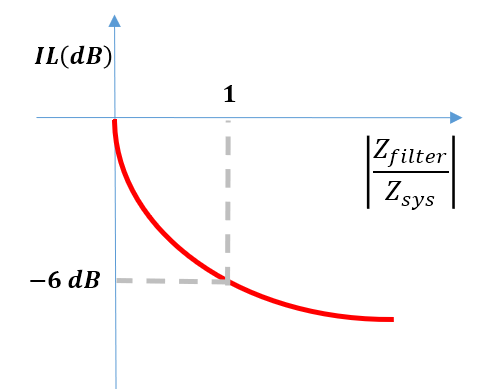

除了在电源线上出现的共模电感应用,在高速信号线上也常常出现共模电感,比如USB3.0,HDMI,LAN等,又或者是一些LVDS的信号线比如CAN BUS,SPI或者RS232,RS485等。在信号线上共模电感的使用,虽然也有抑制共模噪声的作用,比如为了满足某种通信规格所需要的共模抑制比,但是更重要的一点却来自于其附带的电流补偿作用,正如一开始提到的,是电流补偿型共模电感。

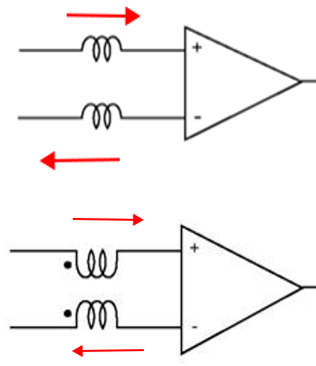

如图Fig.5所示,高速信号线一般采用差分对信号进行传输,信号线上存在电阻,杂散电容和分布电感,通过双绞线的形式可以有效的降低杂散电容但是无法去除分布电感,因此在接收端上存在差模输入电感,线路上的耦合电流会形成信号图上的噪声。这些噪声基于传输线的对称性将接近等量的分布在接收机的两端,现在在接收端输入位置放置共模电感,则接近等量的噪声将通过共模电感的绕组耦合产生抵消,从而极大的降低耦合噪声,也即电流补偿作用使得接收端输入噪声降低。

Fig.5 差分信号沿传输线从发射端到接收端的传输过程(左) 和 在接收端使用共模电感的改善(右)

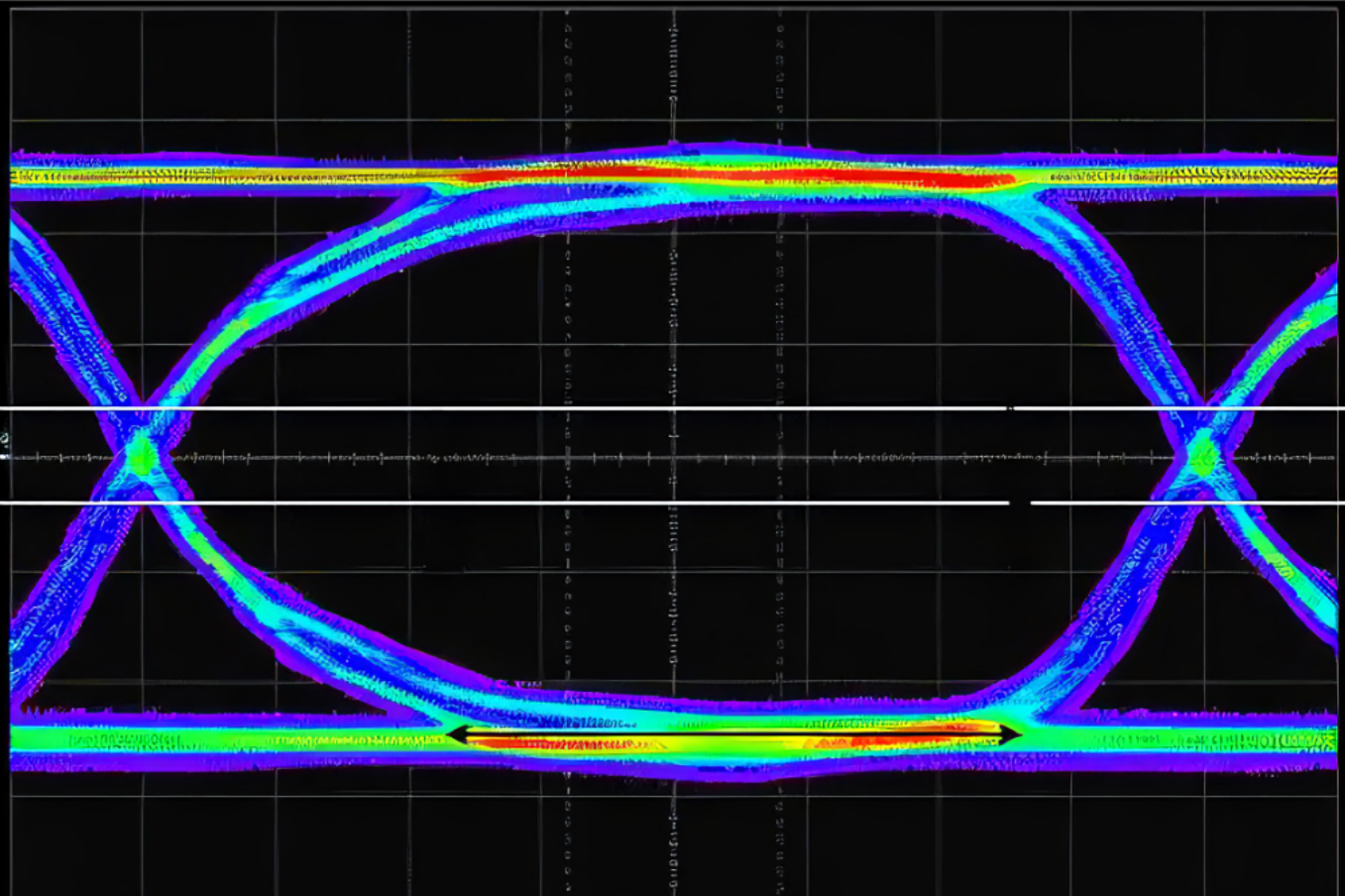

在信号的眼图上可以看到,如Fig.6,通过降低线路杂散感量带来的插入损耗,信噪比将会得到改善,这一点对于更长的传输线或者高速的信号线来说很重要。一般来说,以上提到的信号端口使用的传输线,通常是90~120Ω阻抗的传输线,基于特定的信号带宽要求,一般选用1倍到10倍的阻抗共模电感来提供-6dB到-20dB的共模抑制,这点和前面讲到的电源应用类似,取决于共模噪声回路的阻抗大小,当然随着频率的增高(因为高速信号传输的要求)系统共模阻抗将降低,提供过大的感量将使得滤波带宽变窄,因此需要验证所选择的感量是否匹配高速信号的传输要求。

Fig.6 差分传输线上的线路插入损耗导致信号质量受影响示意图

3 共模噪声的危害

那么,共模噪声究竟有什么问题呢?为什么EMC测试中常常需要重点对回路上的共模噪声进行抑制呢?当然,首先是为了满足各个国家的EMC认证标准,必须对共模和差模信号的幅度进行限制,达到产品的使用安全性同时降低用电侧的电器设备可能产生的对电网的或者对邻域设备的潜在危害。其次,从电源完整性和信号完整性的角度来看,大多数的用电设备与电器的控制器是工作在低压状态的,额外的噪声电压会有可能导致控制信号异常或者传输的数据异常甚至报错和宕机,这些异常干扰既可能来自于线路板上也可能来自其噪声的射频干扰,比如说移动设备掉线或者广播的噪音啸叫。最后,由于超量的共模噪声很可能以高频辐射的形式发射到空间,比如较大的共模回路,或者在天线类似的导体上,对于人身健康是觉察不到的长期危害的。

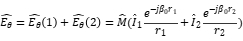

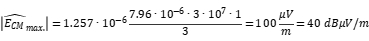

为了简化问题,我们把传输线等效为赫兹磁偶并由此得到如图Fig.7所示的共模噪声辐射模型,测试点距离共模传输线的中心位置距离为d,一般这个距离相比电路的尺寸要大得多因此是远场测试点(Far field),因此对于天线的远场辐射其场强为:

其中: 是对应辐射波长的相位常数,

是对应辐射波长的相位常数, 是测试位置的间距,

是测试位置的间距, 是天线辐射方向图上偏离

是天线辐射方向图上偏离 角度的平面角度,对于赫兹磁偶其

角度的平面角度,对于赫兹磁偶其 且

且 ,这和天线类型有关。由于远点接收到的辐射是共模两条线的同时作用且角度为

,这和天线类型有关。由于远点接收到的辐射是共模两条线的同时作用且角度为 ,于是:

,于是:

对于共模噪声,如图Fig.7: 且

且 ,于是得到测试点上最大辐射为:

,于是得到测试点上最大辐射为:

当线间距s足够小时  于是可以简化为:

于是可以简化为:

因此,共模辐射的强度正比于共模传输线的长度,随着距离的远离减弱。举例说明一下这个幅值的大小:假设共模传输线长度1米,共模电流幅值为7.96µA,对应在30MHz时作为FCC Class B的3米场测试,其辐射强度为:

这个强度刚好就是标准的限额,这时如果在3米测试点位置有1米长度的导体或者人,它将感受到100µV的电压。长期处于这样的环境对于人体健康很很严重的影响,累积的辐射量可能引发各种慢性病或者个体病变,这也是EMC认证的重要意义。

Fig.7 共模噪声的辐射模型与测试点示意图

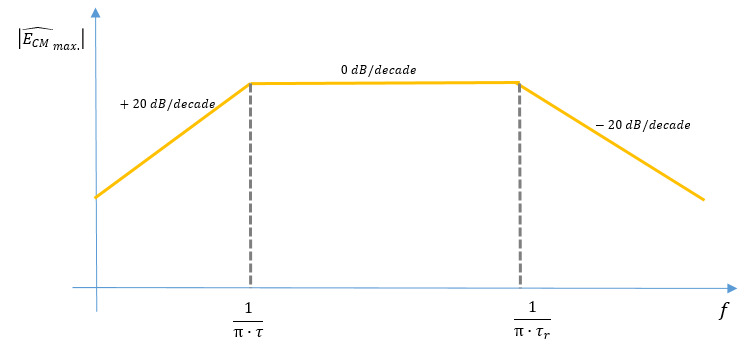

大多数的开关电路上的波形结构可以归为梯形波,其频率谱是随着谐波级数的增加幅值呈现 到

到 两段降速,节点分别是第1角频率和上升沿时间角频率。以上共模的辐射强度的频率谱显然是随频率以

两段降速,节点分别是第1角频率和上升沿时间角频率。以上共模的辐射强度的频率谱显然是随频率以 单增的,因此对于常见的开关电源和方波信号电路,其共模辐射谱将大致如Fig.8图所示,呈现先升后降的分布特点,因此中间段是最需要特别控制或者进行抑制的部分。

单增的,因此对于常见的开关电源和方波信号电路,其共模辐射谱将大致如Fig.8图所示,呈现先升后降的分布特点,因此中间段是最需要特别控制或者进行抑制的部分。

Fig.8 常见梯形波对应的共模噪声辐射强度分布

4 共模电感的选型

对于电源线路,其共模噪声的来源相对比较明确,只是杂散因素难以通过仪器测量,大多数情况下是依赖试验后再进行分析的方式来逐步逼近结果,因此累积的经验非常重要。本文在第2节介绍共模电感的应用时已经讲到理论上对共模噪声的幅度预估和对应的共模电感的感量需求,可以作为早期试验的出发点。

通常情况下,适用在AC-DC电源输入端的滤波阶段的共模电感采用了闭合磁路的磁环作为磁芯,这样做的好处是可以轻松实现非常低的漏感和非常高的耦合系数,对于高输入电压和相对低的开关频率而言可以提供不错的高共模阻抗来抑制较高幅值的共模噪声幅度。由于磁性材料的磁导率可以分为感性部分 和损耗部分

和损耗部分 ,在磁芯接近或者高于阻抗特性最高点时,损耗部分将占据阻抗的主要部分,这时的噪声抑制不再是通过感抗来降低噪声幅度,而是通过损耗发热的形式将噪声能量吸收,因此适当的(过度饱和将导致阻抗降低)饱和程度并不会影响噪声的抑制效果,使得我们在挑选共模电感时不必去寻找类似于功率电感中的饱和电流参数。

,在磁芯接近或者高于阻抗特性最高点时,损耗部分将占据阻抗的主要部分,这时的噪声抑制不再是通过感抗来降低噪声幅度,而是通过损耗发热的形式将噪声能量吸收,因此适当的(过度饱和将导致阻抗降低)饱和程度并不会影响噪声的抑制效果,使得我们在挑选共模电感时不必去寻找类似于功率电感中的饱和电流参数。

同时,如果漏感的部分,比如1mH的电感耦合系数99%那么将会有10uH的漏感存在于差分线路上,当考虑差模噪声抑制(通常是LC滤波桥)时,这一部分漏感也需要考虑在内。适量的漏感对于高频差模噪声抑制有帮助,但是因为共模电感基本上采用的是磁路闭合磁芯,很容易导致在大电流时磁芯饱和,这对电源转换效率和滤波噪声带宽都有影响。提高漏感的占比通常可以选用方形或者框架磁芯结构(UU磁芯或者PQ磁芯等),也可以通过非对称绕组( )来实现,具体的选择需要用户通过差共模分离器鉴别测试后决定是否必要。

)来实现,具体的选择需要用户通过差共模分离器鉴别测试后决定是否必要。

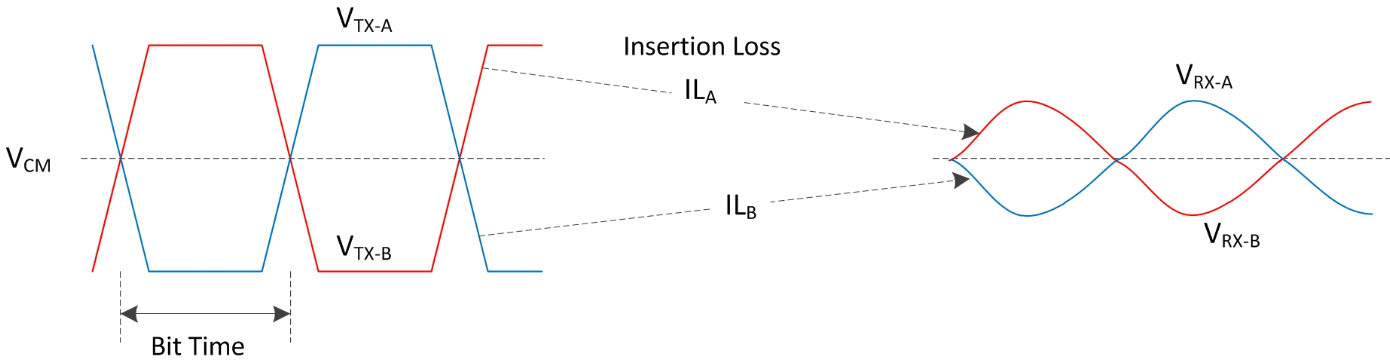

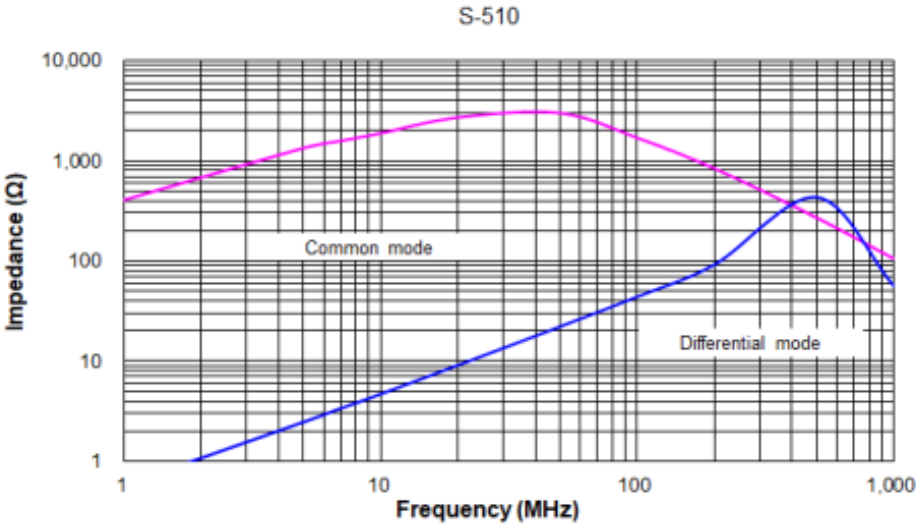

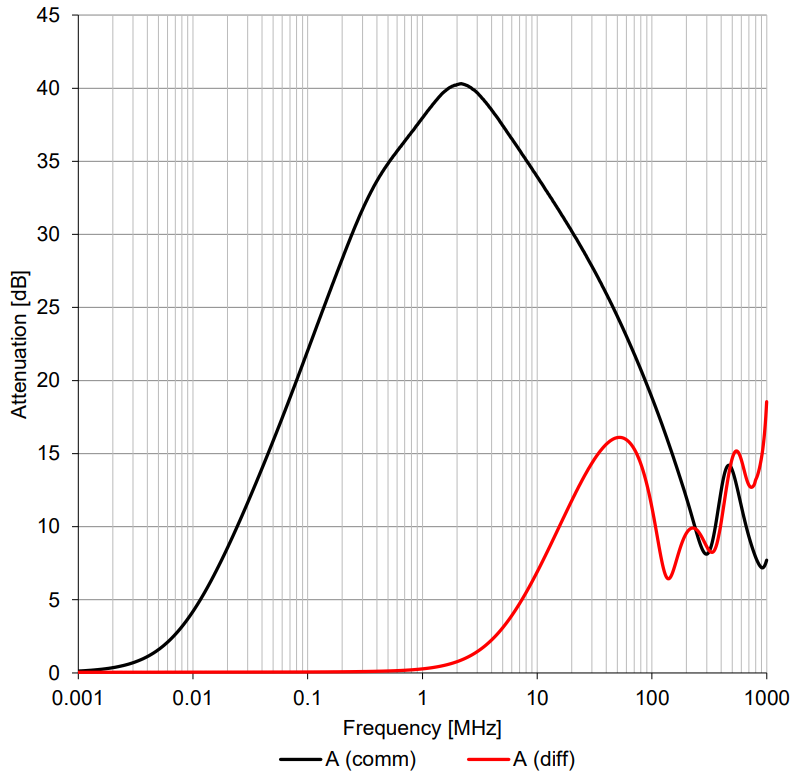

对于共模电感的参数而言,主要包括单边感值,Rdc,额定电流,额定电压和耐压Hi-pot。其中单边感值主要决定了共模阻抗的大小,Rdc是导线的直流损耗,接着损耗带来的温升就产生了额定的电流的限额,最后因为使用在高压线路上所以电压限额和安规要求分别标出。但是用户更希望评估的还是滤波效果,所以一般情况下规格书会提供两种形式的阻抗特性曲线,一是如图Fig.9-a所示的共模/差模阻抗形式,二是如图Fig.9-b所示的插入损耗dB形式,两者是对等的,插入损耗dB形式的曲线是将共模/差模阻抗折算到50Ω+50Ω的系统内形成的。

Fig.9 (a) 共模/差模阻抗形式 (b)插入损耗dB形式

对于同一个共模系列,不同尺寸的封装结构适用不同的电流大小和滤波带宽:尺寸越大,磁芯可以具有更低的磁阻,从而可以减少绕组匝数,这样铜线的线径可以放大因此可以适用更大的电流回路;感值越高或者材料磁导率稳定频率越低,则适用的滤波带宽更窄,这样的共模电感放到回路上很可能对高频端没有噪声抑制效果。

科达嘉电子的共模电感目前主要分信号线和电源线两块,超过10种系列和50种不同的尺寸封装以及接近300款不同的标准料号,广泛适用在诸如CAN BUS,RS485等信号线以及从几瓦到几千瓦的不同离线电源设备,我们的研发技术团队也可以帮忙用户从测试到分析,或者定制适配规格,到最终完成相关的EMC认证。